儋州市网站建设_网站建设公司_安全防护_seo优化

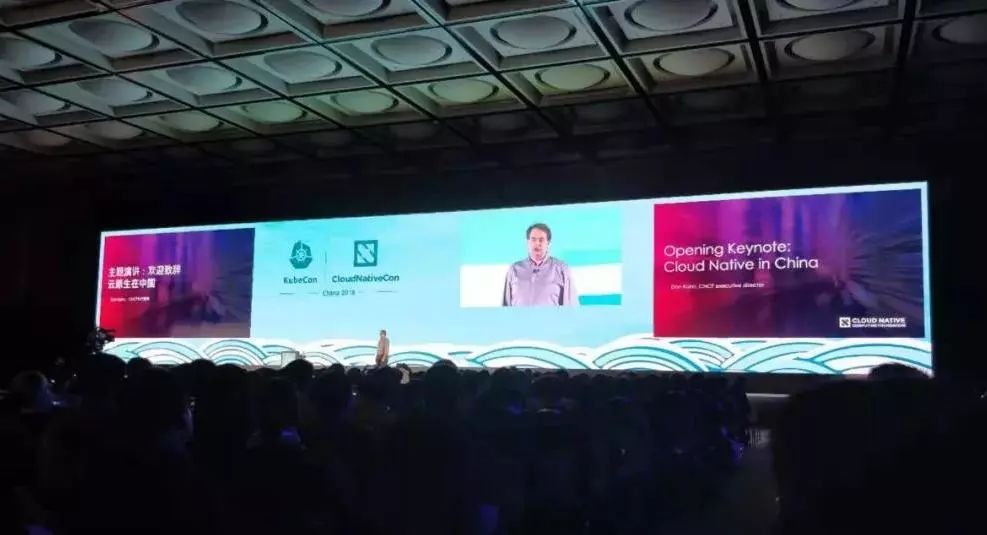

2018年11月13-15日,由云原生计算基金会(CNCF)组织的KubeCon+CloudNativeCon首次登陆中国。经过了三天的技术交流和展示,大会随着15日下午最后一个议程的结束而完美落幕。

作为云原生领域全球最大的峰会,KubeCon+CloudNativeCon大幕打开,就迎来了全球2500多名参会者到场。参会者们与本届大会上160位开发演讲嘉宾(其中中方占1/4)一起,共赴一场Kubernetes引领的云原生技术盛会。

直击大会现场

盛会期间,来自阿里巴巴、eBay、Google、华为、京东、Microsoft、Shopify 等多家公司的专家,针对当今最迫切的云原生话题纷纷发表了演讲。

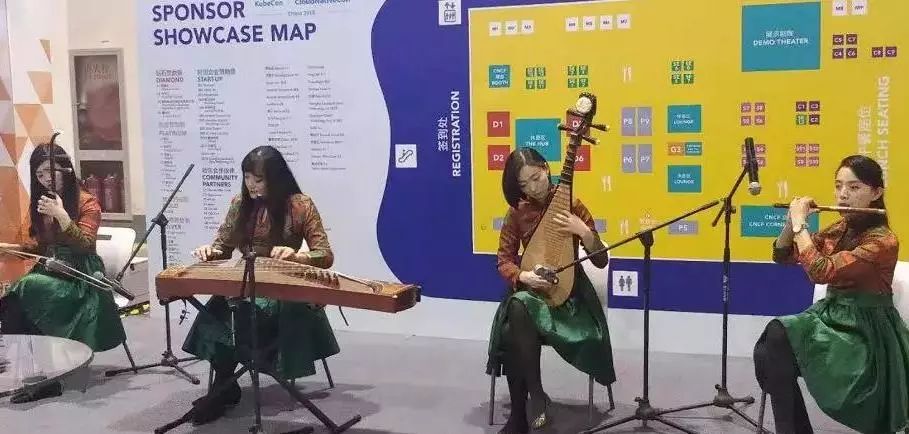

在14号晚上,赞助商欢迎酒会+当地艺人表演吸引了众多参会者的眼球。在白天的主题演中开发者们严肃认真,晚上的酒会和表演又令他们惬意放松。这一松一弛间,尽显盛会之精彩。

(魔术表演)

(魔术表演)

(琴风演奏)

行云之力

行云CTO发表演讲

行云创新CTO马洪喜在15日受邀出席此次大会发表演讲。在大会上,马洪喜通过一个真实的案例——“X项目”的实战经验(为某著名世界500强ICT企业提供核心业务系统微服务改造咨询),从多个方面介绍微服务在落地实践中的宝贵经验,特别是容易步入的误区和陷阱。同时分析微服务和DevOps以及容器技术的内在联系,并对微服务的价值、利弊、成本、产出等多维度进行分析。再结合当下企业的发展态势和挑战,为大家讲述一系列针对性解决方案。

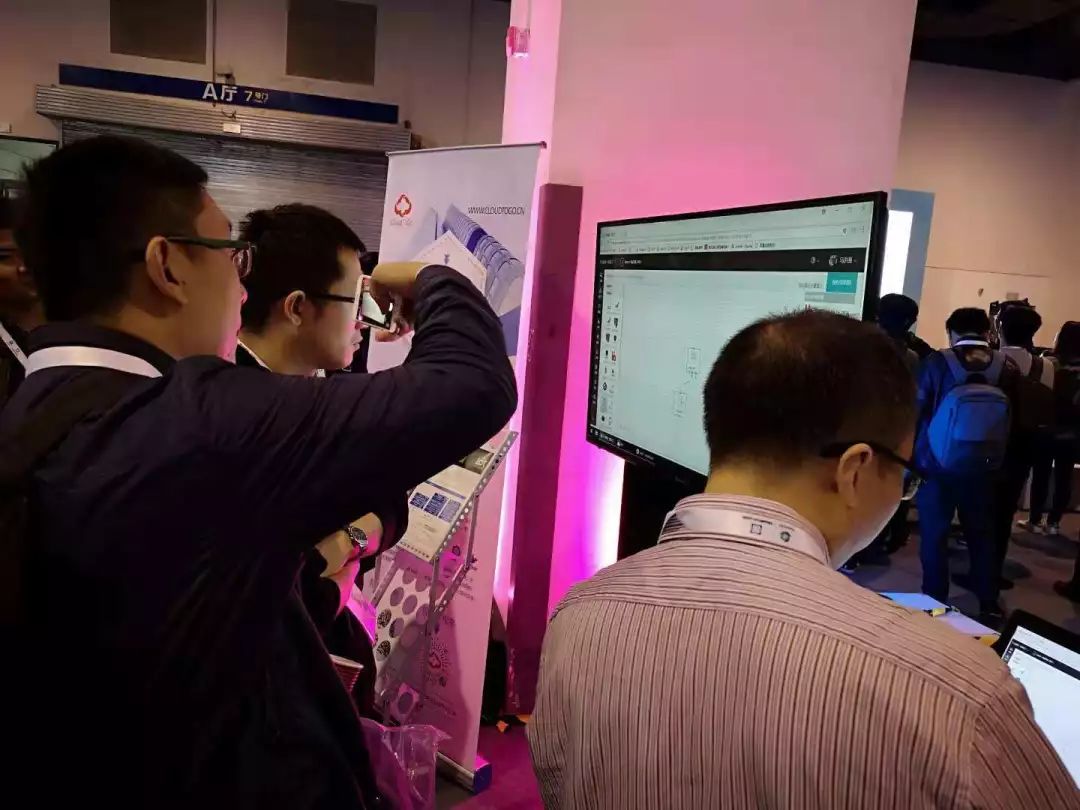

行云展位人头聚集

行云展位面前聚集了众多对行云产品和技术感兴趣的参会者,经过现场人员的讲解和介绍, 参观者表现了极高的兴趣,纷纷表示大开眼界,等待会议结束后使用行云产品。

现场屏幕前,不少开发者掏出手机拍照,认真研究和学习。

(屏幕上为行云产品——趣码应用工厂界面)

2018 KubeCon +CloudNativeCon完美落幕,行云作为中国云原生领域的重要一份子,为大会献出自己的力量。明年六月,KubeCon +CloudNativeCon 还将回到上海召开,进行第二次中国之旅,我们期待下次的相会。

原文地址: https://mp.weixin.qq.com/s/Xd0EMtzbkea4vkSPjaEACQ

.NET社区新闻,深度好文,欢迎访问公众号文章汇总 http://www.csharpkit.com